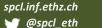

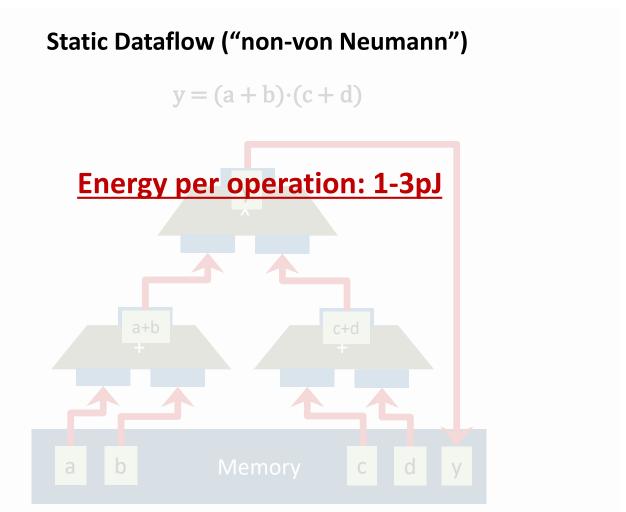

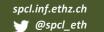

#### Load-store vs. Dataflow

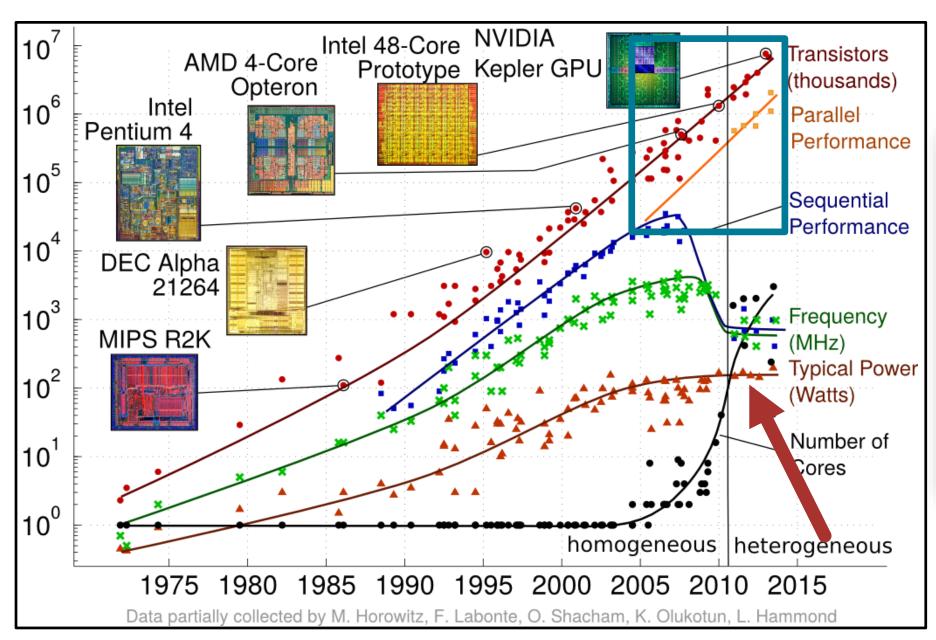

#### **Specialized hardware**

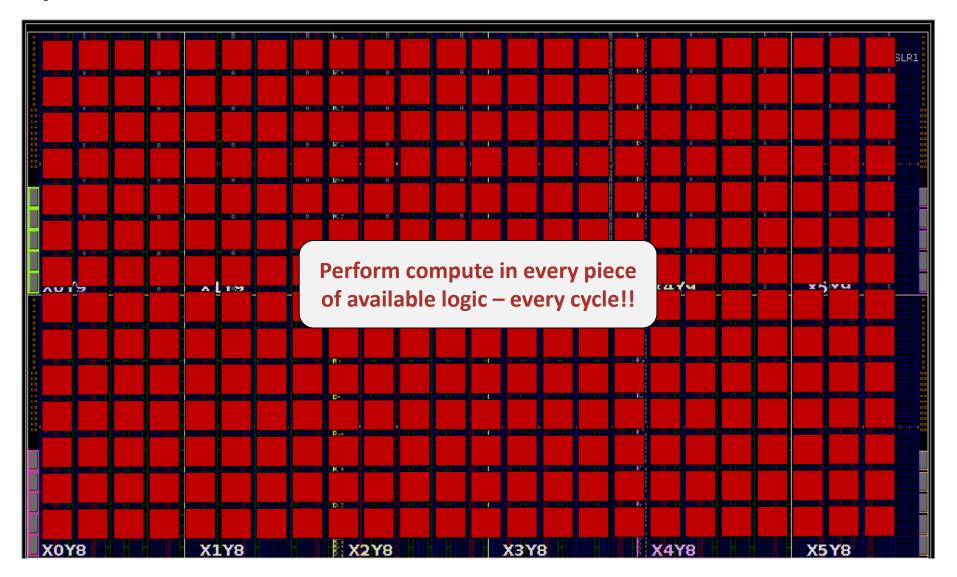

#### The paradox of FPGA efficiency

#### **Specialized hardware**

#### **Traditionally: register transfer level**

```

always @ (posedge clk)

if (start) begin

out <= in + 1;

end</pre>

```

$$int c = a + b;$$

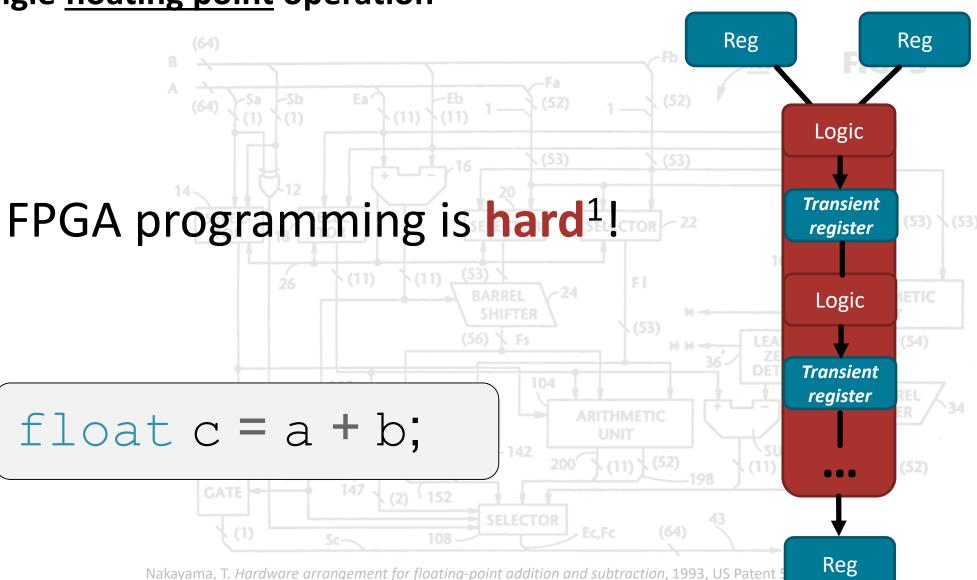

#### Single <u>floating point</u> operation

Nakayama, T. Hardware arrangement for floating-point addition and subtraction, 1993, US Patent!

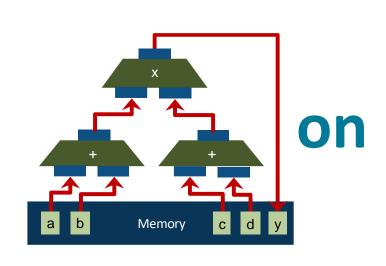

#### **High-level synthesis**

float

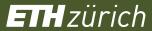

$$y = (a + b) * (c + d);$$

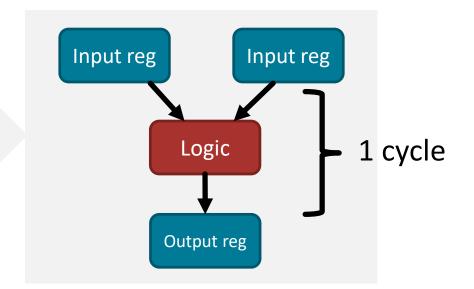

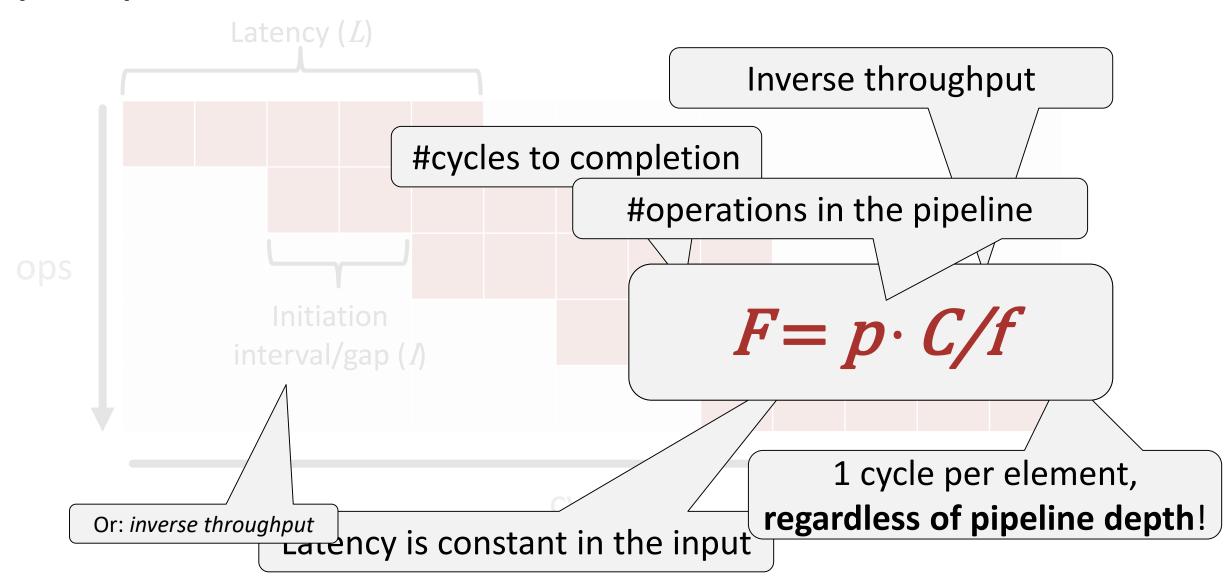

#### **Pipeline performance**

# No matter how deep the pipeline is a new result is produced every cycle

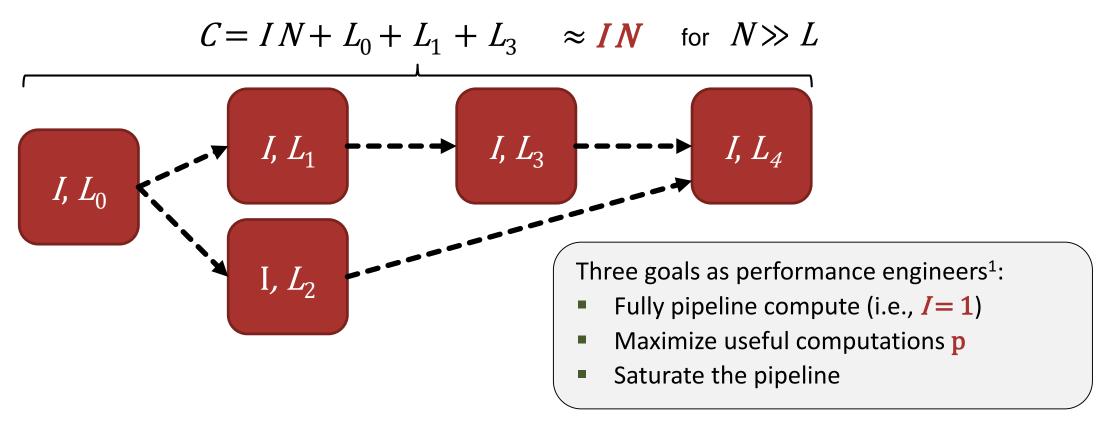

#### End goal: peak!

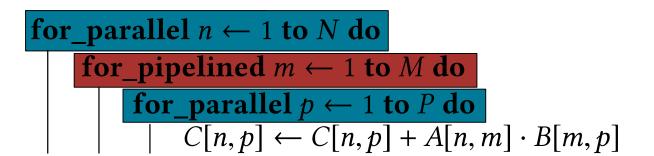

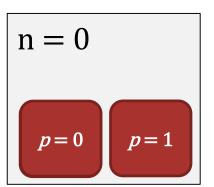

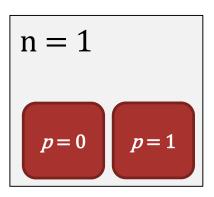

#### **Parallelizing hardware in HLS**

This is now the **full** runtime of the algorith

Parallel loops are **removed** from the iteration space!

$$C \approx IM$$

$$C \approx IM$$

$F = fNP$

Performance corresponds to parallel hardware

#### Parallelizing hardware in HLS

Hardware optimization vs. software optimization?

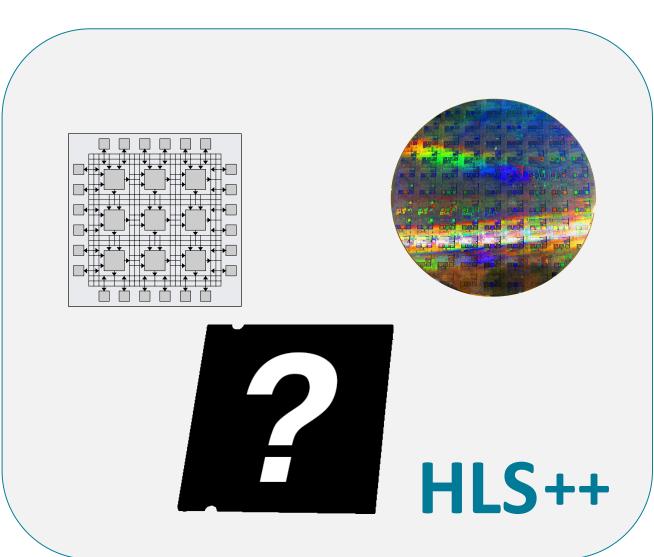

#### Scalability transformations

- Vectorization

- Replication

- Streaming dataflow

# We can implement massively parallel specialized hardware with HLS<sup>1</sup>!

Pipeline colaescing

...but, like GPU-programming, we must be architecture-aware.

- Condition flattening

- Type demotion

- . . . .

### **Hardware scaling**

For HLS, the base case is **bad**  $\ensuremath{\mathfrak{S}}$

|                                            | Perf.    | Speedup          |                 |

|--------------------------------------------|----------|------------------|-----------------|

|                                            | [GOp/s]/ | <b>k</b> elative | Cumulative      |

| Naive                                      | 0.02     | 1×               | _               |

| Buffered [§2.5]                            | 0.8      | $40 \times$      | _               |

| <b>Vectorized</b> [§3.1, §4.2, §4.3, §4.4] | 6.4      | 8×               | $320 \times$    |

| <b>Replicated</b> [§3.2, §3.3, §3.4]       | 227.8    | 36×              | $11,400 \times$ |

[2D stencil]

|                                                     | Perf.   | Speedup     |                 |

|-----------------------------------------------------|---------|-------------|-----------------|

|                                                     | [GOp/s] | Relative    | Cumulative      |

| Naive                                               | 0.01    | 1×          | _               |

| Fused [§2.1, §2.6, §2.7, §4.2]<br>Vectorized [§3.1] | 0.4     | $40 \times$ | _               |

|                                                     |         | 8×          | $320 \times$    |

| <b>Replicated</b> [§3.2, §3.3, §3.4]                | 184.1   | 58×         | $18,410 \times$ |

[Matrix multiplication]

| Luckily, there are patterns ©                                           | Perf.   | Speedup  |            |

|-------------------------------------------------------------------------|---------|----------|------------|

|                                                                         | [GOp/s] | Relative | Cumulative |

| Initial [§4.2, §4.3]                                                    | 0.9     | 1×       | _          |

| Interleaved [§2.2.1]                                                    | 6.0     | 7×       | _          |

| Initial [§4.2, §4.3]<br>Interleaved [§2.2.1]<br>Replicated [§3.2, §3.3] | 231.9   | 39×      | 258×       |

[N-body simulation]

#### **HLS for FPGAs...**

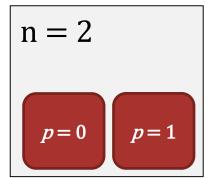

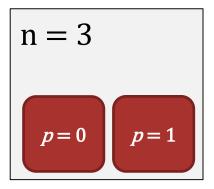

for\_parallel  $n \leftarrow 1$  to N do

| for\_pipelined  $m \leftarrow 1$  to M do

| for\_parallel  $p \leftarrow 1$  to P do

|  $C[n,p] \leftarrow C[n,p] + A[n,m] \cdot B[m,p]$

## ...and beyond?

# Thank you for your attention\*!

\*For more, see:

"Transformations of High-Level Synthesis Codes for High-Performance Computing" [arXiv 1805.08288]